صفيفة البوابات المبرمجة

شهد النصف الثاني من القرن العشرين تطوراً متسارعاً لتكنولوجيا الدارات المتكاملة، ففي العقد السادس منه ظهر الجيل الأول من الدارات المتكاملة الرقمية المُصنَّعة بتقانة transistor transistor logic (TTL) أمّا كثافة التكامل للعناصر الإلكترونية فبقيت منحصرة في التكامل المنخفض المستوى small scale integration (SSI)والمتوسط medium scale integration (MSI). في حقبة السبعينات أزداد عدد الترانزستورات المتكاملة على الشريحة السليكونية فظهرت عناصر تكامل عالي المستوى large scale integration (LSI)، وكانت موجهة أساساً لبعض التطبيقات الخاصة. وإن الاستخدام المحدود لمثل هذه الدارات إضافة إلى تكاليف التصنيع والتصميم التي كانت تزداد بزيادة عدد الترانزستورات حدّت من مستوى تكامل العناصر المنطقية النموذجية (عائلة s74xx) عند المستوى LSIوهذا ما حفز على ظهور عناصر تكامل عالي المستوى جداً very large scale integration (VLSI) استخدمه مصنِّعو أنصاف النواقل لتطوير عائلات متعددة من الدارات المتكاملة، منها العناصر المتكاملة القابلة للبرمجة التي تسمح بتحقيق أي تابع منطقي تركيبياً كان أو تتابعياً مع عدد محدود من المداخل والمخارج، ومن هذه العناصر:

ـ العناصر المنطقية المبرمجةProgrammable Logic Device (PLD).

ـ الصفيفة المنطقية المبرمجةProgrammable Logic Array (PLA).

ـ العناصر المنطقية المبرمجة القابلة للمحي Erasable PLD (EPLD).

ـ صفيفة البوابات المنطقية المبرمجة حقلياً Field Programmable Gate Array (FPGA).

صفيفة البوابات المنطقية المبرمجة من العائلة XC4000 من شركة Xilinx:

ظهرت صفيفة البوابات المنطقية المبرمجة للمرة الأولى في العام 1984، وهي دارات رقمية مسبقة التصميم تتميز بمرونة عالية تسمح برمجتها بإعادة إستخدامها من أجل تحقيق توابع منطقية مختلفة بزمن قصير جداً. وإضافة إلى ذلك فإن التطور التقاني سمح بتصنيع أنواع متطورة من هذه الدارات ذات سرعة أكبر وكثافة تكامل أعلى مما جعلها عناصر أساسية في الكثير من التطبيقات الهامة.

تُصنَّع صفيفة البوابات المنطقية المبرمجة بتقانة CMOS، وتختلف فيما بينها بعدد البوابات المنطقية المشكِّلة لها حيث يصل عدد البوابات المشكلة لأكبر هذه الدارات إلى مليون بوابة قابلة للإستخدام.

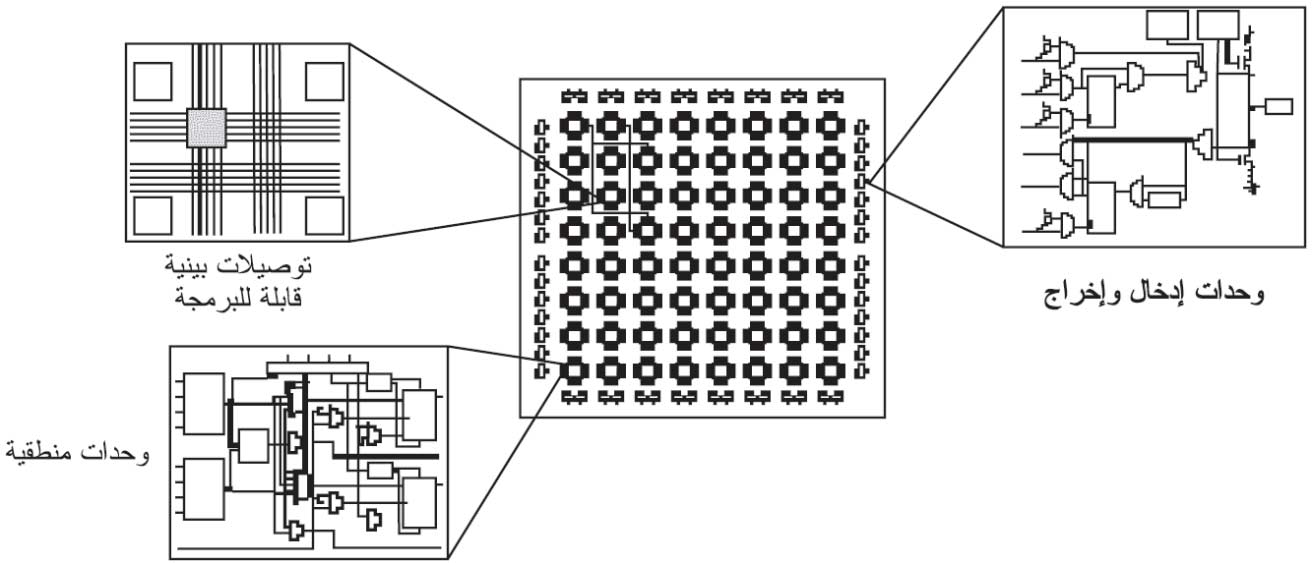

تتألف الصفيفة من هذه العائلة من مصفوفة متناظرة من الوحدات المنطقية المتماثلة القابلة للبرمجة Configurable Logic Block (CLB) محاطة بعدد من وحدات الدخل/خرج Input Output Block (IOB). تترابط الوحدات السابقة فيما بينها بشبكة من الوصلات الداخلية القابلة للبرمجةProgrammable Interconnects، وتجتاز الصفيفة أفقياً وعمودياً كما هو مُوضح في الشكل (1).

تحتوي الصفيفة أيضاً على مهتز تكاملي متوضع في إحدى زوايا الشريحة السليكونية ويمكن تفعيله في مرحلة برمجة الصفيفة، كما يحتوي على دارات عزل موزعة على الزوايا الأربعة للدارة مخصصة لتوزيع إشارة الساعة إلى مختلف الواحدات، وكذلك على مفككات ترميز. وفيما يلي شرح الوحدات الأساسية المُشكلة للصفيفة المذكورة.

1ـ الوحدات المنطقية القابلة للبرمجة: تعد هذه الوحدات الأساس في بناء الصفيفة كما تعد العنصر الرئيس الذي يحدد خصائصها المميزة (الشكل ـ2). تتألف كل واحدة من منطق تركيبي مؤلف من ثلاثة نواخب F,H,G بأربعة مداخل ومن وحدة ذاكرة متزامنة متمثلة بقٌلابين من النوع D. أضف إلى ذلك أنه يوجد في هذه الوحدة أربع مداخل (C1…C4) تسمح بتنفيذ التوصيلات الداخلية بين العناصر المختلفة المشكّلة لهذه الوحدة، وذلك لتحقيق تابع أو توابع منطقية مرغوبة.

يشكل تركيب العناصر السابقة دارة تحتوي على 13مدخلاً و4مخارج. تنقسم المداخل الثلاثة عشر إلى قسمين:

ـ مجموعتين من أربعة مداخل مستقلة (F1…F4) و(G1…G4) تمثل مداخل الناخبينG, F على التوالي. هذا التركيب يسمح للمستثمر بمرونة كبيرة في التصميم، ذلك لأن معظم التوابع المحتملة التصميم بهذه الوحدة لا يتجاوز عدد متحولاتها عن الأربعة. يعدّ خرج الناخبين السابقين نتيجة لبرنامج يعالج مداخلهما مخزناً في ذاكرة الصفيفة.

ـ مجموعة من أربعة مداخل تكميلية (C1…C4) تمثل متحول دخل H1 وثلاث إشارات تحكم DIN, S/R, EC. أما المدخل الثالث عشر فهو مخصص للساعة clock.

أمّا المخارج فتنقسم بدورها إلى مخرجين تركيبيين X وY وآخريين تزامنيينX0 وY0.

يمكن بوساطة هذه الوحدة (CLB) تحقيق أي تابع من التوابع المنطقية الآتية معاً:

ـ تابعين منطقيين بأربع متحولات، وتابع واحد فقط بثلاثة متحولات. ونتائج هذه التوابع الثلاثة مستقلة استقلالاً تاماً إلاٌ أن واحداً منها يجب أن يمر عبر أحد القلابين Dليشكل خرجاً للوحدة CLB.

ـ أي تابع منطقي بخمسة متحولات.

ـ أي تابع منطقي بأربعة متحولات مع بعض التوابع المنطقية بست متحولات.

ـ بعض التوابع المنطقية بتسعة متحولات.

إن تعدد الإمكانيات بتشكيل تابع منطقي باستخدام الوحدة CLB يوفر تحسيناً في سرعة عمل المنظومة كلها.

تُوصل مخارج التركيب المنطقي (مجموعة النواخب F,G,H) إمّا مباشرة إلى مخارج الوحدة CLB عبر الخرجين X (بالنسبة للتابعين F,G) وY (بالنسبة للتابعين G,H) أو إلى مداخل القلابين D0…D1 اللذين يملكان إشارة الساعة وإشارة التأهيل chip enable (CE)، في حين يملك كل قلاب منطقاً خاصاً لتأهيل خرجه على 0 أو1 وبشكل غير تزامني. يعمل هذان القلابان وفقاً لأحد النمطين الآتيين:

ـ نمط قلاب flip-flop حيث تمثل المعطيات اللازم تخزينها إمّا واحداً من التوابع F,G,H أو الدخل DIN.

ـ نمط latch حيث يتم تخزين المعطيات تبعاً للجبهة الصاعدة أو الهابطة لإشارة الساعة. يمثل خرج القلابين السابقين X0, Y0خرجي الوحدة CLB.

أخيراً يمكن أن تستخدم هذه الوحدة ذاكرة ذات نفاذ عشوائي RAM من النوعs32x1bit, 16x1bit أو s16x2bitحيث تمثل المداخل ( F1…F2) و( G1…G2) خطوط العنونة لخلية الذاكرة المعتبرة على حين تمثل المداخل H1,DIN خطوط المعطيات D0…D1 بالنسبة للذاكرة s16x1bit أما المدخل S/Rفيمثل خط تأهيل الكتابة.

2 ـ وحدات الدخل/خرج IOB:تتوزع هذه الوحدات على المحيط الخارجي للصفيفة كما هو موضح بالشكل (1) وتؤمن كل واحدة منها واجهة بينية interface من الصفيفة وتركيب منطقي داخلي مُشكل باستخدام الوحدات CLB. تُستخدم هذه الوحدات دارة دخل أو دارة خرج أو دارة دخل/خرج في آن واحد علماً بأن تهيئة هذه الوحدة للعمل دارة دخل أو دارة خرج يُنفذ بإستخدام ناخب محكوم بإشارة منطقية مؤلفة من خانة واحدة متوضعة في ذاكرة الصفيفة. ويوضح الشكل (3) مخططاً لوحدة الدخل/خرج.

أ ـ تهيئة الوحدة IOB دارة دخل: تجتاز في البداية إشارة الدخل الموجودة على نقطة الدخل/خرج للدارة (Pad) دارة عزل مبرمجة للتوافق مع منطق TTL أو منطقCMOS، ومن ثم يتم قيادة هذه الإشارة نحو مداخل الوحدة المنطقية القابلة للبرمجة (I1…I2) إمّا بشكل مباشر أو عبر دخل تزامني يستخدم قلاباً من النوع D يعمل على الجبهة الصاعدة أو الهابطة، وفي هذه الحالة تُضاف دارة تأخير مناسبة (بضع نانو ثانية) لتعويض التأخير الناتج عن مرور إشارة الساعة عبر المكبر.

ب ـ تهيئة الوحدة IOB دارة خرج: تُميز الخصائص الآتية عندما تعمل هذه الوحدة دارة خرج

ـ يمكن أن تكون إشارة الخرج معكوسة أو لا، وذلك قبل دخولها الى الوحدة IOB.

ـ يمكن تخزين هذه الإشارة عن طريق القلاب D العامل إمّا على الجبهة الصاعدة أو الهابطة لإشارة الساعة.

ـ استخدام الإشارة pull-up وpull-downوذلك بهدف تحديد استهلاك المداخل المخارج غير المستخدمة.

ـ استخدام عازل ثلاثي الحالات three stats buffer محكوم بوساطة الإشارات Out Enable

ـ يمكن لكل خرج تزويد الحمل بتيار مقداره 12ميلي أمبير.

إن الخصائص السابقة الذكر لوحدة الدخل/خرج تسمح للمستثمر باختيار الطريقة الأفضل لوصل التركيب المنطقي الداخلي إلى نقاط الوصل الخارجية.

3 ـ الوصلات الداخلية في صفيفة البوابات المنطقية: تعد الوصلات الداخلية في صفيفة البوابات المنطقية الشرايين التي تصل بين مختلف عناصرها، وهي خطوط معدنية تربط الوحدات المنطقية القابلة للبرمجة فيما بينها من جهة، ومن جهة أخرى تربط هذه الوحدات بوحدات الدخل/خرج كما تستخدم أيضاً من أجل توزيع إشارة الساعة إلى جميع الوحدات عبر دارات عزل متوضعة في الزوايا الأربعة للصفيفة. تشغل الوصلات الداخلية ثلثي مساحة الشريحة السليكونية المخصصة للصفيفة على حين تتوضع العناصر المختلفة الأُخرى على الثلث المتبقي منها. وقد هيأت شركة Xilinx ثلاثة أنواع من الوصلات الداخلية بغية الاستثمار الأفضل للصفيفة لتحقيق دارة معطاة وهي:

ـ الوصلات الداخلية للاستخدام العام: تجتاز مجموعة من الخطوط المعدنية الصفيفة أفقياً وعامودياً بالتناوب مع الوحدات المنطقية القابلة للبرمجة ووحدات الدخل/خرج. تتقاطع هذه المجموعات في نقاط تدعى مصفوفات التماس القابلة للبرمجة Switch Matrix كما هو موضح في الشكل (4). تُبرمج هذه المصفوفات لتأمين الاتصال بين خطوط معينة وذلك بغية تحقيق تابع أو توابع منطقية مرغوبة عن طريق ترانزستورات من نوع MOS متحكم بها عن طريق خلايا ذاكرة من نوع RAM.

ـ الوصلات الداخلية المباشرة: تسمح هذه الخطوط بالوصل المباشر للوحدات المنطقية القابلة للبرمجة فيما بينها ووصلها مباشرة أيضاً بوحدات الدخل/خرج من أجل تحقيق فعالية عظمى من وجهة نظر السرعة والاستثمار الأفضل للصفيفة بالنسبة لدارة ما. ويمثل الشكل (5) رسماً توضيحياُ لهذه الوصلات.

ـ الخطوط الطويلة: وهي خطوط معدنية تمتد على طول الصفيفة وعرضها. تسمح عند الحاجة بنقل الإشارة بتأخير زمني شبه معدوم، كما تسمح بتجنب تكرار نقاط التماس من أجل تحقيق وصلة معينة، ويوضح الشكل (6) نموذجاً لهذه الوصلات.

برمجة صفيفة البوابات المنطقية

لا تملك الصفيفة برنامجاً محدداً يصف عملها فمن الضروري إذاً برمجتها في كل مرة يراد استخدامها من أجل تحقيق تابع أو توابع منطقية مرغوبة. تَبرمج الصفيفة بوساطة برنامج مكتوب بإحدى لغات وصف البنية المادية (VHDL, Verilog, ABEL,.) الذي يُخزن في ذاكرة RAM موجودة داخل الصفيفة مخصصة لهذه الغاية.

نضال زيدان

شهد النصف الثاني من القرن العشرين تطوراً متسارعاً لتكنولوجيا الدارات المتكاملة، ففي العقد السادس منه ظهر الجيل الأول من الدارات المتكاملة الرقمية المُصنَّعة بتقانة transistor transistor logic (TTL) أمّا كثافة التكامل للعناصر الإلكترونية فبقيت منحصرة في التكامل المنخفض المستوى small scale integration (SSI)والمتوسط medium scale integration (MSI). في حقبة السبعينات أزداد عدد الترانزستورات المتكاملة على الشريحة السليكونية فظهرت عناصر تكامل عالي المستوى large scale integration (LSI)، وكانت موجهة أساساً لبعض التطبيقات الخاصة. وإن الاستخدام المحدود لمثل هذه الدارات إضافة إلى تكاليف التصنيع والتصميم التي كانت تزداد بزيادة عدد الترانزستورات حدّت من مستوى تكامل العناصر المنطقية النموذجية (عائلة s74xx) عند المستوى LSIوهذا ما حفز على ظهور عناصر تكامل عالي المستوى جداً very large scale integration (VLSI) استخدمه مصنِّعو أنصاف النواقل لتطوير عائلات متعددة من الدارات المتكاملة، منها العناصر المتكاملة القابلة للبرمجة التي تسمح بتحقيق أي تابع منطقي تركيبياً كان أو تتابعياً مع عدد محدود من المداخل والمخارج، ومن هذه العناصر:

ـ العناصر المنطقية المبرمجةProgrammable Logic Device (PLD).

ـ الصفيفة المنطقية المبرمجةProgrammable Logic Array (PLA).

ـ العناصر المنطقية المبرمجة القابلة للمحي Erasable PLD (EPLD).

ـ صفيفة البوابات المنطقية المبرمجة حقلياً Field Programmable Gate Array (FPGA).

صفيفة البوابات المنطقية المبرمجة من العائلة XC4000 من شركة Xilinx:

ظهرت صفيفة البوابات المنطقية المبرمجة للمرة الأولى في العام 1984، وهي دارات رقمية مسبقة التصميم تتميز بمرونة عالية تسمح برمجتها بإعادة إستخدامها من أجل تحقيق توابع منطقية مختلفة بزمن قصير جداً. وإضافة إلى ذلك فإن التطور التقاني سمح بتصنيع أنواع متطورة من هذه الدارات ذات سرعة أكبر وكثافة تكامل أعلى مما جعلها عناصر أساسية في الكثير من التطبيقات الهامة.

تُصنَّع صفيفة البوابات المنطقية المبرمجة بتقانة CMOS، وتختلف فيما بينها بعدد البوابات المنطقية المشكِّلة لها حيث يصل عدد البوابات المشكلة لأكبر هذه الدارات إلى مليون بوابة قابلة للإستخدام.

|

| الشكل (1) التركيب الداخلي لصفيفة البوابات المنطقية المبرمجة من العائلة XC4000 |

تحتوي الصفيفة أيضاً على مهتز تكاملي متوضع في إحدى زوايا الشريحة السليكونية ويمكن تفعيله في مرحلة برمجة الصفيفة، كما يحتوي على دارات عزل موزعة على الزوايا الأربعة للدارة مخصصة لتوزيع إشارة الساعة إلى مختلف الواحدات، وكذلك على مفككات ترميز. وفيما يلي شرح الوحدات الأساسية المُشكلة للصفيفة المذكورة.

|

| الشكل (2) الوحدة المنطقية القابلة للبرمجة CLB |

يشكل تركيب العناصر السابقة دارة تحتوي على 13مدخلاً و4مخارج. تنقسم المداخل الثلاثة عشر إلى قسمين:

ـ مجموعتين من أربعة مداخل مستقلة (F1…F4) و(G1…G4) تمثل مداخل الناخبينG, F على التوالي. هذا التركيب يسمح للمستثمر بمرونة كبيرة في التصميم، ذلك لأن معظم التوابع المحتملة التصميم بهذه الوحدة لا يتجاوز عدد متحولاتها عن الأربعة. يعدّ خرج الناخبين السابقين نتيجة لبرنامج يعالج مداخلهما مخزناً في ذاكرة الصفيفة.

ـ مجموعة من أربعة مداخل تكميلية (C1…C4) تمثل متحول دخل H1 وثلاث إشارات تحكم DIN, S/R, EC. أما المدخل الثالث عشر فهو مخصص للساعة clock.

أمّا المخارج فتنقسم بدورها إلى مخرجين تركيبيين X وY وآخريين تزامنيينX0 وY0.

يمكن بوساطة هذه الوحدة (CLB) تحقيق أي تابع من التوابع المنطقية الآتية معاً:

ـ تابعين منطقيين بأربع متحولات، وتابع واحد فقط بثلاثة متحولات. ونتائج هذه التوابع الثلاثة مستقلة استقلالاً تاماً إلاٌ أن واحداً منها يجب أن يمر عبر أحد القلابين Dليشكل خرجاً للوحدة CLB.

ـ أي تابع منطقي بخمسة متحولات.

ـ أي تابع منطقي بأربعة متحولات مع بعض التوابع المنطقية بست متحولات.

ـ بعض التوابع المنطقية بتسعة متحولات.

إن تعدد الإمكانيات بتشكيل تابع منطقي باستخدام الوحدة CLB يوفر تحسيناً في سرعة عمل المنظومة كلها.

تُوصل مخارج التركيب المنطقي (مجموعة النواخب F,G,H) إمّا مباشرة إلى مخارج الوحدة CLB عبر الخرجين X (بالنسبة للتابعين F,G) وY (بالنسبة للتابعين G,H) أو إلى مداخل القلابين D0…D1 اللذين يملكان إشارة الساعة وإشارة التأهيل chip enable (CE)، في حين يملك كل قلاب منطقاً خاصاً لتأهيل خرجه على 0 أو1 وبشكل غير تزامني. يعمل هذان القلابان وفقاً لأحد النمطين الآتيين:

ـ نمط قلاب flip-flop حيث تمثل المعطيات اللازم تخزينها إمّا واحداً من التوابع F,G,H أو الدخل DIN.

ـ نمط latch حيث يتم تخزين المعطيات تبعاً للجبهة الصاعدة أو الهابطة لإشارة الساعة. يمثل خرج القلابين السابقين X0, Y0خرجي الوحدة CLB.

أخيراً يمكن أن تستخدم هذه الوحدة ذاكرة ذات نفاذ عشوائي RAM من النوعs32x1bit, 16x1bit أو s16x2bitحيث تمثل المداخل ( F1…F2) و( G1…G2) خطوط العنونة لخلية الذاكرة المعتبرة على حين تمثل المداخل H1,DIN خطوط المعطيات D0…D1 بالنسبة للذاكرة s16x1bit أما المدخل S/Rفيمثل خط تأهيل الكتابة.

|

| الشكل (3) وحدة الدخل / الخرج IOB |

أ ـ تهيئة الوحدة IOB دارة دخل: تجتاز في البداية إشارة الدخل الموجودة على نقطة الدخل/خرج للدارة (Pad) دارة عزل مبرمجة للتوافق مع منطق TTL أو منطقCMOS، ومن ثم يتم قيادة هذه الإشارة نحو مداخل الوحدة المنطقية القابلة للبرمجة (I1…I2) إمّا بشكل مباشر أو عبر دخل تزامني يستخدم قلاباً من النوع D يعمل على الجبهة الصاعدة أو الهابطة، وفي هذه الحالة تُضاف دارة تأخير مناسبة (بضع نانو ثانية) لتعويض التأخير الناتج عن مرور إشارة الساعة عبر المكبر.

|

| الشكل (4) الوصلات الداخلية للأستخدام العام مع رسم توضيحي لمصفوفة التماس القابلة للبرمجة |

ـ يمكن أن تكون إشارة الخرج معكوسة أو لا، وذلك قبل دخولها الى الوحدة IOB.

ـ يمكن تخزين هذه الإشارة عن طريق القلاب D العامل إمّا على الجبهة الصاعدة أو الهابطة لإشارة الساعة.

ـ استخدام الإشارة pull-up وpull-downوذلك بهدف تحديد استهلاك المداخل المخارج غير المستخدمة.

ـ استخدام عازل ثلاثي الحالات three stats buffer محكوم بوساطة الإشارات Out Enable

ـ يمكن لكل خرج تزويد الحمل بتيار مقداره 12ميلي أمبير.

إن الخصائص السابقة الذكر لوحدة الدخل/خرج تسمح للمستثمر باختيار الطريقة الأفضل لوصل التركيب المنطقي الداخلي إلى نقاط الوصل الخارجية.

|

| الشكل (5) الوصلات الداخلية المباشرة |

|

| الشكل (6) الخطوط الطويلة |

ـ الوصلات الداخلية للاستخدام العام: تجتاز مجموعة من الخطوط المعدنية الصفيفة أفقياً وعامودياً بالتناوب مع الوحدات المنطقية القابلة للبرمجة ووحدات الدخل/خرج. تتقاطع هذه المجموعات في نقاط تدعى مصفوفات التماس القابلة للبرمجة Switch Matrix كما هو موضح في الشكل (4). تُبرمج هذه المصفوفات لتأمين الاتصال بين خطوط معينة وذلك بغية تحقيق تابع أو توابع منطقية مرغوبة عن طريق ترانزستورات من نوع MOS متحكم بها عن طريق خلايا ذاكرة من نوع RAM.

ـ الوصلات الداخلية المباشرة: تسمح هذه الخطوط بالوصل المباشر للوحدات المنطقية القابلة للبرمجة فيما بينها ووصلها مباشرة أيضاً بوحدات الدخل/خرج من أجل تحقيق فعالية عظمى من وجهة نظر السرعة والاستثمار الأفضل للصفيفة بالنسبة لدارة ما. ويمثل الشكل (5) رسماً توضيحياُ لهذه الوصلات.

ـ الخطوط الطويلة: وهي خطوط معدنية تمتد على طول الصفيفة وعرضها. تسمح عند الحاجة بنقل الإشارة بتأخير زمني شبه معدوم، كما تسمح بتجنب تكرار نقاط التماس من أجل تحقيق وصلة معينة، ويوضح الشكل (6) نموذجاً لهذه الوصلات.

برمجة صفيفة البوابات المنطقية

لا تملك الصفيفة برنامجاً محدداً يصف عملها فمن الضروري إذاً برمجتها في كل مرة يراد استخدامها من أجل تحقيق تابع أو توابع منطقية مرغوبة. تَبرمج الصفيفة بوساطة برنامج مكتوب بإحدى لغات وصف البنية المادية (VHDL, Verilog, ABEL,.) الذي يُخزن في ذاكرة RAM موجودة داخل الصفيفة مخصصة لهذه الغاية.

نضال زيدان